## **EE105 – Fall 2014 Microelectronic Devices and Circuits**

Prof. Ming C. Wu wu@eecs.berkeley.edu 511 Sutardja Dai Hall (SDH)

Lecture22-Multistage Amplifiers(2)

1

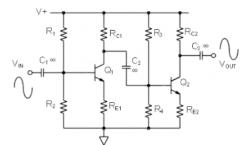

## **AC-Coupled CE Amplifiers**

- · Discussed in Lecture 21

- Each stage has independent DC bias

- Cannot achieve very low frequency response

- e.g., Lab 5 and 6 use DC coupling

Lecture22-Multistage Amplifiers(2)

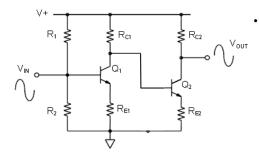

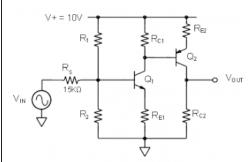

### **DC-Coupled Cascaded Common-Emitter Amplifiers**

- In DC coupled multistage cascaded CE amplifiers, the output bias level of each stage increases to maintain the collector more positive than the base

- If this voltage "stacking" is severe, little head room is left in the final stages of the cascade.

Lecture22-Multistage Amplifiers(2)

3

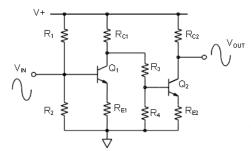

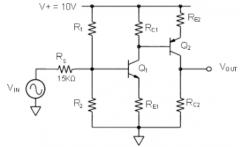

#### **DC-Coupled Cascaded Common-Emitter Amplifiers**

- The R<sub>3</sub>, R<sub>4</sub> resistor divider not only reduces the signal amplitude seen at the base of Q<sub>2</sub>, it also reduces the DC bias level from the collector of Q<sub>1</sub> to a more manageable DC level at the base of Q<sub>2</sub>.

- This happens at the cost of overall signal gain in the combined amplifier.

Lecture22-Multistage Amplifiers(2)

4

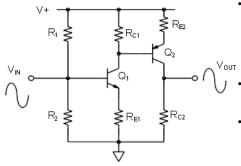

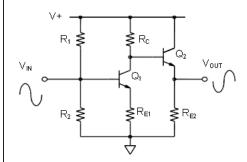

#### **Complementary Pair Amplifier**

- Having both polarities of transistors allows for more flexibility in how amplifier sages can be combined and can make biasing easier as well.

- First stage: NPN CE Second stage: PNP CE

- By using complementary devices, active level shifting can be combined with amplification

- The p-stage collector DC operating point tends to cancel the bias level "stacking" issue we encountered in the all NPN CE amplifier

Lecture22-Multistage Amplifiers(2)

5

# Complementary Pair Amplifier – Design Example

- Design a Complementary Pair amplifier stage using 2N3904 and 2N3906 transistors

- $-\beta \sim 120, V_{BE} \sim 0.7V$

- $V_{cc} = 10V$

- $-R_s = 15 K\Omega$

- Question:

- Estimate the DC bias voltages

- Determine the small signal gain at1 KHz

Lecture22-Multistage Amplifiers(2)

6

### **Complementary Pair Amplifier – Design Example**

DC bias:

$$V_{EQ} = V_{CC} \frac{R_2}{R_1 + R_2} \qquad \qquad R_B = R_1 \parallel R_2$$

$$V_{C1} \approx \frac{V_{EQ} - 0.7V}{R_R / \beta + R_{F1}}$$

$V_{C1} \approx V_{CC} - I_{C1}R_{C1}$

$$I_{C1} \approx \frac{V_{EQ} - 0.7V}{R_B / \beta + R_{E1}}$$

$$I_{C2} \approx \frac{V_{CC} - V_{C1} - 0.7V}{R_{E2}}$$

Small-signal gain:

Both  $Q_1$  and  $Q_2$  are CE with degeneration:

$$A_{V1} = -\frac{g_{m1}R_{C1}}{1 + g_{m1}R_{E1}} \approx -\frac{R_{C1}}{R_{E1}}$$

$$A_{V2} \approx -\frac{R_{C2}}{R_{E2}}$$

$$A_{V} = \frac{R_{B}}{R_{S} + R_{B}} \left( \frac{R_{C1}}{R_{E1}} \right) \left( \frac{R_{C2}}{R_{E2}} \right)$$

$$R_B = R_1 \parallel R_2 \parallel (r_\pi + (1 + \beta)R_{E1}) \approx R_1 \parallel R_2$$

Lecture22-Multistage Amplifiers(2)

#### **DC-Coupled CE-CC Amplifier**

$$I_{C1} = \frac{V_{EQ} - 0.7V}{R_B / \beta + R_{E1}}$$

$$V_{C1} = V_{CC} - I_{C1}R_C$$

$$I_{C2} = \frac{V_{C1} - 0.7V}{R_{E2}}$$

· Input stage: CE

- High R<sub>in</sub>

Moderate to high gain

· Output stage: CC

- Low Rout

· Overall gain is nearly independent of load resistance and source resistance

· Multiple CE stages can be cascaded with CC stages inserted between them to reduce the attenuation due to inter-stage loading

· Direct coupling is commonly used in IC because this saves biasing resistors

Lecture22-Multistage Amplifiers(2)